74ls153全加器电路图,74ls153全加器电路图真值表

这种级联方式形成的是串行结构74ls153全加器电路图,处理速度相对较慢,若需实现并行快速相加,则可以采用超前进位加法全加器是组合逻辑电路中最基本且应用广泛的组件之一,通常用于实现带有低位进位的加法运算根据组合逻辑电路的设计方法,可以进行全加器功能的详细设计通过使用逻辑门74LS138译码器以及74LS153D数据选择器等。

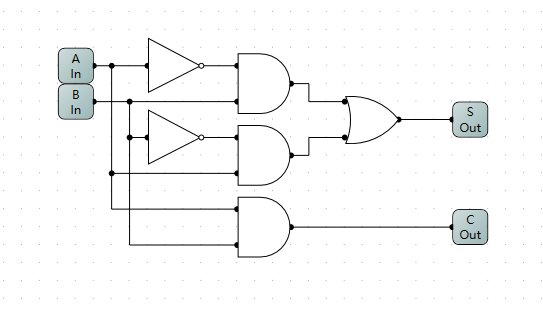

全加器的逻辑功能是两个同位的二进制数及来自低位的进位三者相加全加器用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器一位全加器可以处理低位进位,并输出本位加法进位多个一位全加器进行级联可以得到多位全加器常用二进制四位全加器74LS283。

474LS153 一片双四选一数据选择器574LS04 一片六反向器674LS283 一片四位二进制全加器774LS20 三片双4输入与非门 五预习要求1 提前预习实验内容及相关知识2 自行设计电路列写必要的真值表表达式,画出接线图实验四 时序电路实验 一实验目的1 掌握边沿JKFF的功能。

用74LS153设计一个一位全加器,方法如下1首先根据全加器真值表,写出和S高位进位C1的逻辑函数S=A?B?C02A1A0作为两个输入变量即加数和被加数AB,D0~D3作为第三个输入变量即低位进位C0,1Y为全加器的和S,2Y为全加器的高位进位C1,于是就可以令数据选择器的输入为A1=A,A。

A1A0作为两个输入变量,即加数和被加数AB,D0~D3为第三个输入变量,即低位进位CI,1Y为全加器的和S,2Y全加器的高位进位CO,则可令数据选择器的输入为 A1=A,A0=B,1DO=1D3=CI,1D1=1D2=CI反,2D0=0,2D3=1,2D1=2D2=CI,1Q=S1,2Q=CO可以根据管脚所对应的连接电路。

74LS153是个双路4进1出的多路开关这里的3输入全加器的实现,本质上就是用2个输入把4种结果预制,然后加上第3个输入作为变量这个实验电路仅仅起到教学作用,大概是帮助学生74ls153全加器电路图了解多路开关的,从成本和复杂度上并不具备任何实用性专用的全加器不香吗为啥把74LS153这种淘汰货从棺材里翻出来。

相关标签 :